## Low Power, High Performance Sigma-Delta Digital to Analog Converter

#### **FEATURES**

- Low Noise : 6 nv √hz Typ

- Low Distortion : -105 dB Typ, -100 dB Max

- Low Power : 1.5 mA Typ

- Operation from -55 C° to +200 C°

- Wide Reference Range : 1 Volt to 2.5 Volts

- Wide clock rate range : 64 Kbit to 512 KBit

- Small 14 pin dip bathtub package

- Flexible Power Supply : + 5 V to  $\pm$  6 V

#### **APPLICATIONS**

Precision A/D calibration source

TX5309

- Seismic Systems calibration source

- Precision Waveform generator

- Laboratory Instruments

- Embedded signal source

- Downhole Logging

### DESCRIPTION

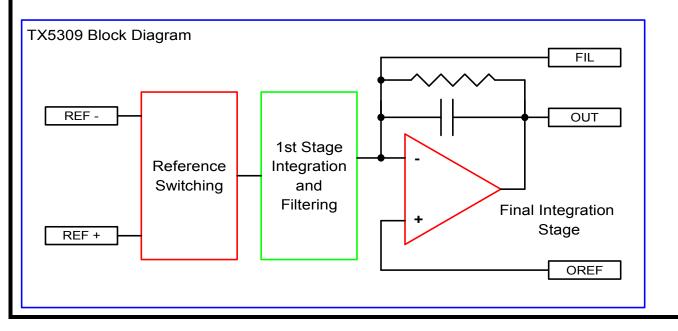

The TX5309 is a precision sigma-delta DAC designed to produce high quality analog representations of a 'ones-density' bit stream and data clock. The device is flexible over a wide range of power supply voltages and reference inputs and features extremely low power operation. The TX5309 has an output reference pin (OREF) which is useful for referencing, or offsetting the output to a desired voltage. The TX5309 also provides connections for additional external filtering and output scaling to reduce clock feed thru even further and permit fine adjustment of the output. **The TX5309 is rated for operation over a temperature range of -55 C° to +200 C°.**

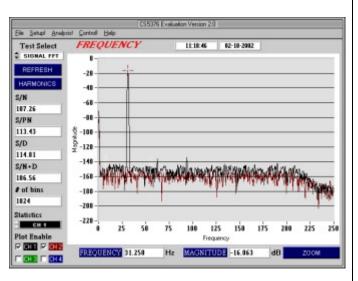

#### Typical Performance Plot @ 512 Kbits / Sec

Typical performance data. Channel 2 is a shorted input to display system noise floor.

#### TX5309 Pinout (top view)

| OUT  | • | 0 | 14 |

|------|---|---|----|

| NC   | 0 | 0 | 13 |

| FIL  | 0 | 0 | 12 |

| V-   | 0 | 0 | 11 |

| DGND | 0 | 0 | 10 |

| DATA | 0 | 0 | 9  |

| REF+ | 0 | ٥ | 8  |

Dimensions(max) : 0.5" W X 0.8" L X 0.15" H Case is Hermetic metal bathtub

All-metal package provides an effective faraday shield for the internal circuitry.

# TX5309 specifications @ ±5V, >= 10K Load and 25C°

| Distortion           | -100 dB Max at 512 Kb / Sec                                                         |

|----------------------|-------------------------------------------------------------------------------------|

| Linearity            | ± 2 Lsb                                                                             |

| Output Noise         | 8 nV √hz max                                                                        |

| Output @ 512 Kb / S  | Vref / 2 [ Peak - Peak ] ( ± 1 % )                                                  |

| Output @ 256 Kb / S  | -3 db Relative to output at 512 Kb / Sec                                            |

| Output @ 128 Kb / S  | -6 dB Relative to output at 512 Kb / Sec                                            |

| Output Offset        | ± 125 Microvolts max                                                                |

| OREF Bias Current    | ± 50 nA max                                                                         |

| Reference Input      | 1.0 Volt to 2.50 Volts                                                              |

| Reference Type       | Fully Differential                                                                  |

|                      | Reference inputs may be anywhere between the power rails                            |

| Positive Supply      | +3 Volts to + 6 Volts @ 1.5 mA max @ +5 Volts                                       |

| Negative Supply      | 0 Volts to – 6 Volts @ 1.5 mA max @ -5 Volts                                        |

|                      | A minimum of 5 V is required between the supplies for specified operation.          |

|                      | Any combination which satisfies this requirement is acceptable up to $\pm$ 6 volts. |

| Digital Inputs       | 3.3 to 5 volt logic                                                                 |

| Data Clock Feed thru | 25 mV (P-P) max @ 512 Kb / Sec data rate                                            |

### **APPLICATION NOTES**

The TX5309 uses switched capacitor techniques to implement this DAC function. Several precautions should be observed to insure proper device performance.

1) Current spikes are present at the reference inputs and should be bypassed with high quality capacitors. Remember that these inputs are effectively signal inputs. Any dielectric dissipation in the bypass caps can introduce significant distortion.

2) If this device shares clock sources with a high resolution delta-sigma digitizer, a slight delay should be added to the DATA and CLK paths to insure that the TX5309 does not introduce artifacts into the digitizing system.

- 3) Reference selection is critical. The chosen reference should have low noise and excellent transient response.

- 4) Proper supply bypassing should be implemented to achieve maximum device performance.

# Using the TX5309

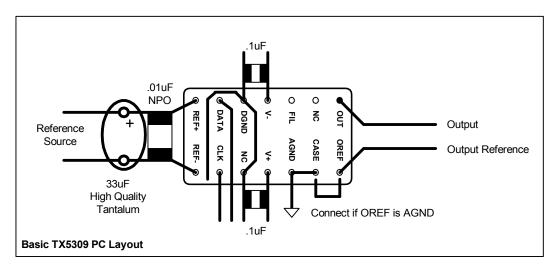

Below is a layout example for the TX5309. Key features of proper operation consist of the following :

- The reference inputs should be bypassed with high quality capacitors as close as possible to the package pins. The 33uF electrolytic should be a low dielectric loss tantalum capacitor. The .01uF capacitor will swamp most of the switching transients and should be an NPO type.

- 2) The DATA and CLK pins should be shielded by digital ground on both sides of the board, around the pins, to prevent digital feed through to the reference inputs.

- 3) Digital supply bypassing should be near the package. A 10 ohm resistor may be inserted in series with the supply lines in order to further isolate switching transients.

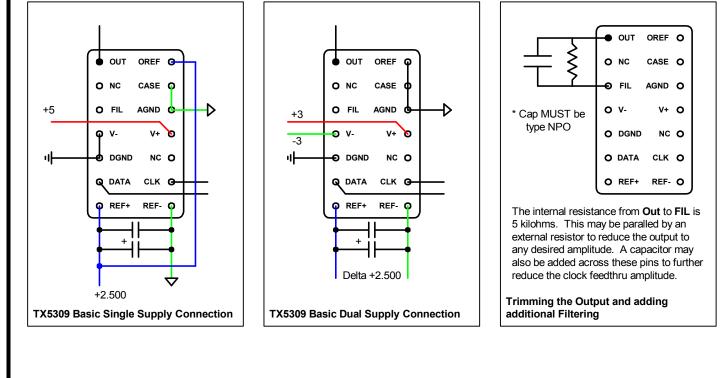

The TX5309 may be used with both single and dual supplies and trimmed as shown below.